你的位置:亚博体彩官方网站入口 > 亚博滚球 >

亚博体彩app 2D、2.5D与3D封装时代的辞别与利用

发布日期:2026-02-15 12:03 点击次数:57

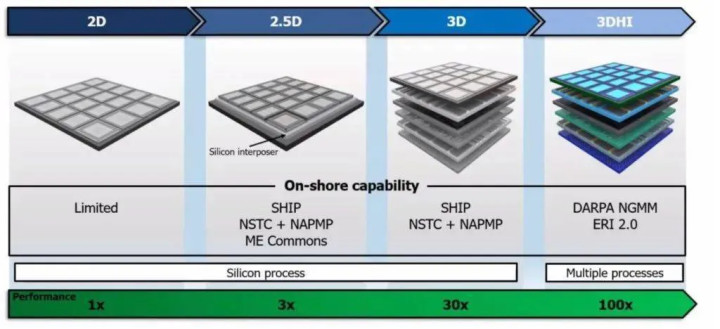

半导体封装时代的发展历久遵从着摩尔定律的延迟与超越。当制程工艺靠拢物理极限,先进封装时代成为延续芯片性能提高的要害旅途。本文将从时代旨趣、典型结构和利用场景三个维度,系统瓦解2D、2.5D及3D封装的时代互异。

一、传统2D封装的平面集成

手脚最老练的封装神气,2D封装弃取引线键合(Wire Bonding)或倒装焊(Flip Chip)口头,将芯片水平排布在基板名义。其中枢特征是悉数互连齐发生在XY平面内,通过基板的金属布线层已毕芯片间通讯。以常见的QFP封装为例,芯片通过金线与外围引脚邻接,最终用环氧树脂塑封成型。这种结构上风在于工艺老练、老本便宜,但受限于平面布局,当集成多颗芯片霎会导致封装面积急剧增大,且互连长度增多带来信号延迟和功耗高涨问题。当今仍庸碌利用于微闭幕器、功率器件等对集成度条目不高的规模。

二、2.5D封装的硅中介层改进

2.5D封装通过引入硅中介层(Interposer)已毕时代跃迁。该时代将芯片比肩排布在带有TSV(硅通孔)的硅中介层上,中介层既提供高密度互连布线,又通过TSV已毕垂直标的的电气邻接。以台积电CoWoS(Chip on Wafer on Substrate)为例,其硅中介层布线密度可达传统PCB基板的100倍以上,线宽/线距可作念到0.4μm/0.4μm。这种结构特别合乎HBM高带宽内存与逻辑芯片的集成,举例NVIDIA的GPU通过2.5D封装将HBM2显存与GPU中枢的互连距离缩小至毫米级,带宽提高至传统GDDR决策的5倍以上。但硅中介层的制造需要特殊工艺行径,导致老本比传统封装高出30-50%。

三、3D封装的垂直堆叠阻挠

3D封装平直将芯片或芯片层在Z轴标的堆叠,通过TSV已毕垂直互连。三星的V-NAND闪存即是典型代表,亚博体彩其将128层存储单位垂直堆叠,单位间距仅几十纳米。更复杂的3D IC如AMD的3D V-Cache时代,弃取搀和键合(Hybrid Bonding)将64MB SRAM缓存堆叠在贪图芯片上方,互连密度达到每闲居毫米10^6个邻接点,探询延迟责骂至传统片外缓存的1/3。这种结构最大上风是大幅缩小互连长度,使得数据传输能耗责骂达90%,但濒临散热挑战,需要配套缔造微流体冷却等新式散热决策。

四、时代对比与演进趋势

从集成密度来看,2D封装互连密度约10²/cm²,2.5D提高至10⁴/cm²,而3D封装可达10⁶/cm²。在延迟进展上,3D封装的垂直互连使信号传输旅途缩小至微米级,较2D封装的厘米级旅途有量级提高。老本方面,2D封装每闲居厘米约0.1好意思元,2.5D因硅中介层升至1-2好意思元,3D封装则需3-5好意思元。刻下时代演进呈现交融态势:Intel的Foveros Direct时代将2.5D中介层与3D堆叠集合,已毕40μm间距的面对面键合;台积电SoIC时代则通过晶圆级键合使堆叠过错小于1μm。往日跟着搀和键合、光互连等时代的发展,封装时代将络续向异质集成、超短距互连标的演进,鼓励算力密度阻挠新的物理极限。

备案号:

备案号: